Earlier this year, Elon Musk’s Neuralink demonstrated an implantable brain-computer interface (BCI) capable of recording electrophysiological activity from several thousands of biological neurons with high fidelity and signal resolution. Such implantable BCIs offer avenues to treating debilitating neurological disorders (e.g., they are already being used to predict the onset of seizures, bouts of anxiety, depression, and risk of suicide), controlling prostheses (e.g., by deducing movement intent and thereby controlling prosthetic limbs that mimic the activity of biological limbs), enhancing memory (e.g., via hippocampal BCIs), turning “thoughts” into speech, and much more.

While Neuralink presents a technical milestone in permitting high-fidelity recording of an unusually large number of biological neurons, it is not unique in concept – recent years have seen a surge in the number of next-generation implantable BCI prototypes developed in both academic labs, and also in industry. Companies like Kernel, Mindmaze, Longeviti, Neuropace, Neurable, Medtronic, and CTRL-Labs (which Facebook has just announced the acquisition of), along with Neuralink, are developing BCIs for many research and medical uses. In fact, there are already several hundreds of individuals with FDA-approved implantable BCIs nationally.

Principled computer architecture techniques will be vital to unlock the full range of brain-computer interactions that BCIs offer. Modern BCIs are domain-specific (i.e., they generally treat a particular class of diseases in a particular brain region, or enable a particular technology), and there is a need to build more general-purpose BCI platforms. In this article, we will discuss the reasons for today’s fragmented BCI ecosystem, and how computer architects can offer a more principled and general-purpose alternative by leveraging “accelerator-level parallelism” reminiscent of mobile SoCs and increasingly, the high-performance computing space.

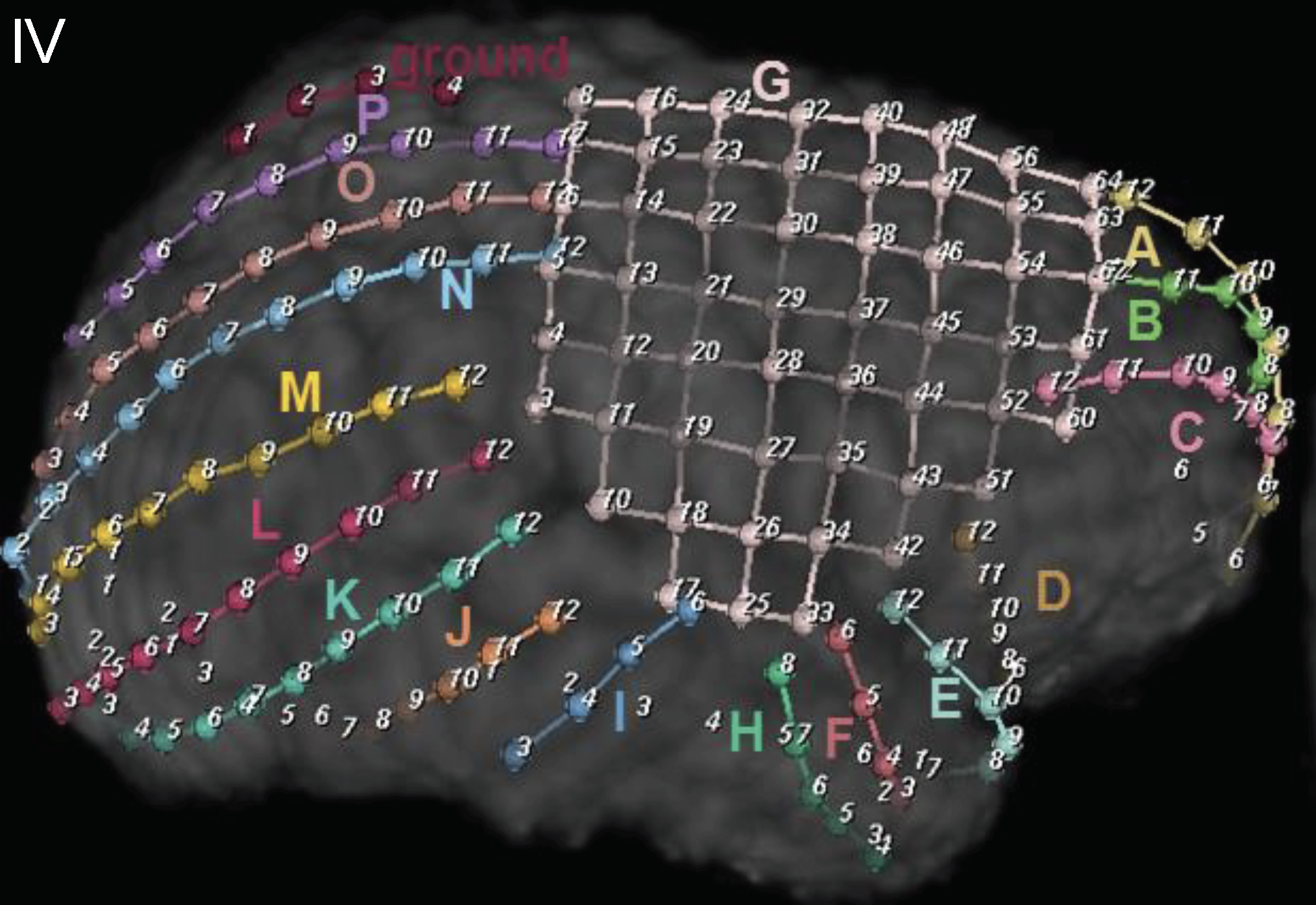

Intra-cranial electrodes in an epilepsy patient. The electrodes shown are (G), an 8×8 contact grid electrode; (A-F, H-P) subdural strip electrodes. At Yale, we place an average of 200 electrode contacts per patient. (Courtesy of Drs. Dennis Spencer and Hitten Zaveri.)

Why Implantable BCIs are Specialized

Chronically implanted BCIs must not heat up brain tissue by more than 1°C, which translates to power budgets of 15 to 40mW (depending on target brain region and depth of implantation). Dissipating more power damages the cellular structure of brain tissue. One might, in principle, consider using a non-invasive BCI instead, but these devices record noisy brain signals that are less than ideal for forward-looking applications.

Unfortunately, meeting these power constraints is challenging as implantable BCIs require real-time performance on large streams of neuronal data. At Yale, for example, our collaborators in the neurosurgery department place an average of 200 electrodes on patients with epilepsy (see Figure) and read neuronal activity at 30KHz with 20-bit samples, corresponding to 120Mpbs of neural data. To put this in context, Netflix and Amazon recommend roughly 15-20Mpbs to stream 4K Ultra HD videos. Neuralink’s threads push this number to 1000Mbps, and efforts like DARPA’s NESD, which target millions of neuronal channels, would theoretically result in data rates of hundreds of Gbps. Consider, further, that many of the medical uses for these devices require real-time responsiveness. For example, for individuals with epilepsy, the BCI has to process incoming data streams to predict or detect seizures and stimulate the brain in response (to mitigate the seizure) within milliseconds. Similarly, BCIs that control prosthetic limbs require millisecond turnaround times to mimic the responsiveness of biological limbs.

To achieve the target power efficiency for these high data rates, BCI developers have either designed highly specialized hardware (to treat only a specific class of diseases in a particular brain region), or have completely eschewed processing hardware (e.g., Neuralink’s initial prototype includes only the analog front-end to process neuronal data thus far). Looking ahead, data rates will continue rising in order to increase coverage of different brain regions. Such coverage is essential as there is evidence that structural and functional networks across brain centers influence the manifestation of pathologies like epilepsy. Consequently, the BCI ecosystem is likely to become intractably fragmented without a ground-up rethink of BCI architectures.

The Pitfalls of Over-Specialization

Unfortunately, the domain-specificity of BCIs precludes their wider adoption. Consider, for example, that treating even one disorder can require implantation in different brain regions, ranging from the dorsal and orbital prefrontal cortices to the amygdala, hypothalamus, and ventral striatum (among others). These regions use different biological neural circuits and require different types of signal processing. Furthermore, not all BCIs are targeted at brain tissue; in fact, some emerging BCIs are being used for implantation in the spinal cord, where they can offer electrical stimulation to facilitate muscle contractions and improve spinal cord injury recovery. Additionally, patients with one neurological disorder often suffer from others too. For example, patients diagnosed with epilepsy are eight times as likely to develop Alzheimer’s disease, three times as likely to develop Parkinson’s disease, and twenty-nine times as likely to commit suicide. Unfortunately, domain-specific BCIs cannot handle this wide heterogeneity of diseases and use cases today, not to mention the fact that each of these diseases can manifest themselves in different patients in different ways.

We believe that there is a real need for a single principled platform architecture that is general-purpose (so that it can be used for many brain regions and end-goals), safe (so that it does not overheat brain tissue), robust to sensor and hardware failures (so that it passes FDA regulations), high-performance (so that it can meet real-time performance demands), and modular (so that it can continue to integrate added functionality as scientists learn more about the brain).

A Call to Arms for Computer Architects

We believe that computer architects are well placed to facilitate a disciplined and principled approach to BCI development. In particular, we may be able to leverage the lessons learned from our experience architecting mobile SoCs, and increasingly, heterogeneous architectures for high-performance domains. There are several classic architecture questions that can guide the design of a more flexible and general-purpose BCI platform:

How do we balance specialization and general-purpose capabilities? A viable approach may be to identify a set of commonly-used computational kernels used in BCIs, so that they can be realized with highly power-efficient implementations. In tandem, we envision integrating a low-power embedded micro-controller to handle less frequently-used computation. One way of thinking about this might be to consider the classic control/data plane separation — i.e., the data plane is realized using hardware accelerator blocks, while the control plane is implemented on a low-power micro-controller. Computer architects are well placed to answer questions such as – What are the commonly-used computational kernels needed? Can they be decomposed into a canonical set of sub-kernels that might be shared among larger processing pipelines? How should hardware realizations of these kernels be connected? What kind of general-purpose core should be allied with the specialized hardware blocks?

What implications does the choice of general-purpose micro-controller have? There exist several choices of general-purpose micro-controllers or DSPs that might fit our power constraints. However, could there be benefits to leaning on open-source eco-systems like RISC-V for this work? The open-source nature of the ISA and architectures may be particularly suitable for the “auditing” requirements of the FDA approval process. If this is the case, what kinds of formal verification techniques should we investigate to ascertain the correct and safe functionality of the emerging open-source hardware paradigm?

How do we manage accelerator-level parallelism? Hill & Reddi’s recent SIGARCH blog post on accelerator-level parallelism offers many questions pertinent to the design of principled BCI platforms. How should accelerators communicate on platforms that are even more power-constrained than mobile SoCs? Data movement clearly has to be minimized but additionally, many of the capabilities that need to be realized on this platform must meet real-time constraints. How can we build these guarantees into the general hardware flow of these devices? How do we guarantee performance isolation in situations where the BCI handles many concurrent activities (e.g., stimulation for epilepsy and anxiety/depression)?

Answers to these questions will likely require greater crosstalk between neuroscientists and computer systems experts than has traditionally been the case. (Stay tuned for announcements on a SIGARCH visioning workshop that includes this topic!) We expect this crosstalk to be vital to the development of next-generation BCIs, and to more broadly offer a window into computer architecture for biomedical devices. Furthermore, implantable BCIs present a particularly data-intensive exemplar of IoT devices with extreme levels of accelerator-level parallelism; developing a principled approach to architecting these devices will shed light on architectures for emerging IoT domains more broadly.

About the author: Abhishek Bhattacharjee is an Associate Professor of Computer Science at Yale University. His research interests are centered on topics at the interface of architecture, operating systems, and compilers. Through the lens of these topics, he is currently working on next-generation brain-computer interfaces and modeling frameworks for cognitive neuroscience.

Disclaimer: These posts are written by individual contributors to share their thoughts on the Computer Architecture Today blog for the benefit of the community. Any views or opinions represented in this blog are personal, belong solely to the blog author and do not represent those of ACM SIGARCH or its parent organization, ACM.