by Yuhao Zhu on Sep 13, 2022 | Tags: Systems, Vision, Wetware

René Descartes, inspired by anatomical observations of nerve fibers, suggested in his monumental work Principles of Philosophy that (in modern terms) visual stimuli of the external world are captured and transmitted as fluids traveling through nerve fibers, leading to...

Read more...

by Mingyu Gao on Aug 29, 2022 | Tags: graduate school, Machine Learning, phd, Research

Modern research in computer architecture has been developed far beyond the conventional textbook topics of processor microarchitectures and memory hierarchies, now expanding to a much more diverse range of novel areas. Computer architects can explore many promising...

Read more...

by Irene Zhang on Aug 24, 2022 | Tags: datacenter, microkernel, Networking, Operating Systems, os

The research community has long predicted the death of Moore’s law and attendant growth in datacenter hardware speeds. In a few years, datacenter networks will grow an order of magnitude from 40Gb to 400Gb. Systems researchers, including myself, have been preparing...

Read more...

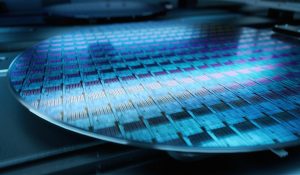

by Caroline Trippel on Aug 15, 2022 | Tags: Datacenters, Errors, Reliability, Testing

Hyperscalers are reporting frequent silent data corruptions (SDCs)—a.k.a. silent errors or corrupt execution errors (CEEs)—in their cloud fleets caused by silicon manufacturing defects. Notably, SDCs at-scale exhibit error occurrence rates on the order of one fault...

Read more...

by Dana Vantrease and Lisa Hsu on Aug 12, 2022 | Tags: Education, Industry

One of the unexpected side effects of the COVID-19 pandemic was the opportunity to virtually co-teach Computer Architecture at Princeton University during the spring of 2021. Princeton was in need of an instructor, and given that everything was over Zoom anyway, they...

Read more...

by Emery Berger on Aug 10, 2022 | Tags: Academia, Education, Machine Learning

CS educators: AI-based developer tools are gunning for your assignments. Resistance is futile GitHub’s AI-based Copilot tool went public this summer. It’s an amazing tool for software developers. But students armed with it will be bringing Uzis to a knife fight. Using...

Read more...

by Richard L. Sites on Aug 8, 2022 | Tags: Cache, Prefetching

Cache prefetching is a well-studied topic, but we continue to strive for improvement. Two small ideas are presented here, one for software prefetching and one for hardware. Bigger software prefetches When I worked at Google, a survey of fleet execution time revealed...

Read more...

by Koji Inoue on Aug 4, 2022 | Tags: Emerging Technology, Nanophotonics, Quantum Computing, Superconductor Computing

Computing technology entering a new phase Computers have evolved over half a century into an essential and indispensable backbone of social information infrastructure. And now, it faces a significant turning point. Although Moore’s Law, which doubles the number...

Read more...

by Alexander Hankin, Lillian Pentecost, Marco Donato, Mark Hempstead, Gu-Yeon Wei, and David Brooks on Aug 3, 2022 | Tags: Memory, Modelling, non-volatile, Persistent, Tools

Non-volatile memory technologies have a rich past dating back to the 1960s. Fairchild R&D Lab member Chih-tang Sah first noted in 1961 the ability of electric charge to remain on the surface of an electrical device for up to several days. By the 1970s the first...

Read more...

by Abhishek Bhattacharjee on Jul 29, 2022 | Tags: Accelerators, Brain computer interface, Signal Processing

In mid-July of this year, Synchron, a brain-computer interface (BCI) startup, announced that it had partnered with Mount Sinai West in New York to permanently implant a stent-like BCI in the motor cortex of a paralyzed patient and read neurological signals to capture...

Read more...