“The theory behind open source is simple. In the case of an operating system, the source code is free. Anyone can improve it, change it, exploit it. But those improvements, changes, and exploitations have to be made freely available.”

– Linus Torvalds

The advent of open-source software has revolutionized the software industry. It has reduced engineering costs and sped up development cycles. This allows small teams of developers to quickly implement their ideas using open-source tools, packages, libraries, etc. Inspired by the collaborative ethos of open-source software, agile and open-source chip development has gained traction in academic and industry over the past decade. The Architecture 2030 Workshop in 2016, held in conjunction with ISCA, laid the groundwork for envisioning hardware design mirroring the accessibility of software, essentially making HW as easy to design/write as SW. Building on this vision, ISCA 2019’s SIGARCH Visioning Workshop brought together leading minds to explore “Agile and Open Hardware for Next-Generation Computing“. The subsequent release of the 2020 IEEE MICRO magazine’s special issue, “Agile and Open-Source Hardware” showcased significant strides in the field. Today, open-source chip design and development has evolved from theory to reality, poised to reshape technology paradigms.

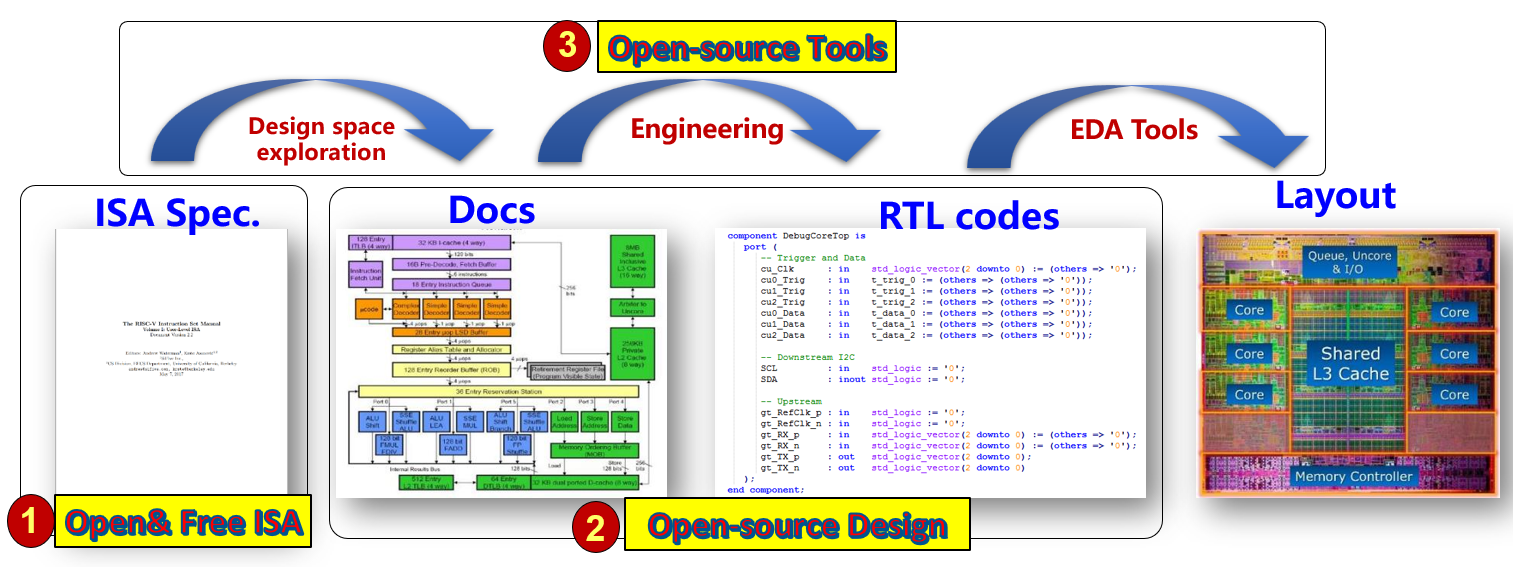

In contrast to the open-source software ecosystem, which values in the tens of billions of dollars, the open-source chip ecosystem remains in its infancy. As depicted in Figure 1, the traditional way to develop a processor entails three primary stages:

1) Formulate the microarchitecture design in alignment with an instruction set architecture (ISA) specification.

2) Implement the microarchitecture design, with significant engineering efforts, usually Register Transfer Level (RTL) coding to describe the circuits.

3) Translate RTL into a physical chip layout with electronic design automation (EDA) tools, preparing for taping out.

Figure 1. Open Source Chip Ecosystem = Open&Free ISA + Open-source Design + Open-source Tools

Despite the notable influence of the open-source RISC-V architecture in the ecosystem, a substantial gap remains between the ISA and the completion of a chip design. In fact, to establish a comprehensive open-source chip ecosystem, it is essential to address three levels of open-sourcing, as illustrated in Figure 1.

L1: Open & Free ISA – ISAs serve as specifications, which should be freely accessible, allowing any entity to utilize them for the design and implementation of processors without constraints. Examples of Level 1 entities include RISC-V.

L2: Open-Source Design – Implementation level details should be freely available for access, such as source codes, documents, etc. Numerous open-source chip projects, such as RocketChip, BOOM, and XiangShan, fall within this category.

L3: Open-Source Tools – Design and verification tools, platforms, and other essential tools should be open-source. Examples of Level 3 entities include OpenRoad, iEDA and agile development methodology (also known as MinJie).

It is widely acknowledged that RISC-V, belonging to Level 1 (L1), has made a profound impact on a global scale. However, the number of successful open-source chip projects in L2 an L3 remains limited, akin to the prominence of Linux and GCC/LLVM in the open-source software domain. PULPino developed at ETH Zurich is an open-source single-core microcontroller system based on 32-bit RISC-V cores. RocketChip and BOOM originated from UC Berkeley and have been widely adopted. Recently, XiangShan and agile development methodology MinJie, both of which are open-sourced and freely accessible (published in MICRO‘22 and selected as IEEE MICRO Top Picks) attained widespread acceptance within the industry.

The latest generation V3 of XiangShan has emerged as the highest-performing CPU among all open-source processors, laying a competitive foundation for future research in computer architecture. On one hand, the development of XiangShan processors overcomes significant challenges, fostering an environment conducive to innovation. On the other hand, XiangShan, with MinJie development tool, exemplifies the feasibility of this new development approach, potentially encouraging wider adoption among research and development teams. As showcased in our MICRO’22 paper, a third-year Ph.D. student efficiently implemented a microarchitecture technique on XiangShan within hours and validated its effectiveness using MinJie tools. Furthermore, industry backing facilitates routine tape-out plans to identify and certify silicon-proven research ideas, accelerating collaboration between academia and industry. As an open source tool, MinJie has integrated various development toolchains and will continue to develop new tools like power modeling, formal verification, and secure enclave tools. Coupled with XiangShan, it holds the potential to serve as an active platform for validating novel methodologies on real-world, large-scale chip designs.

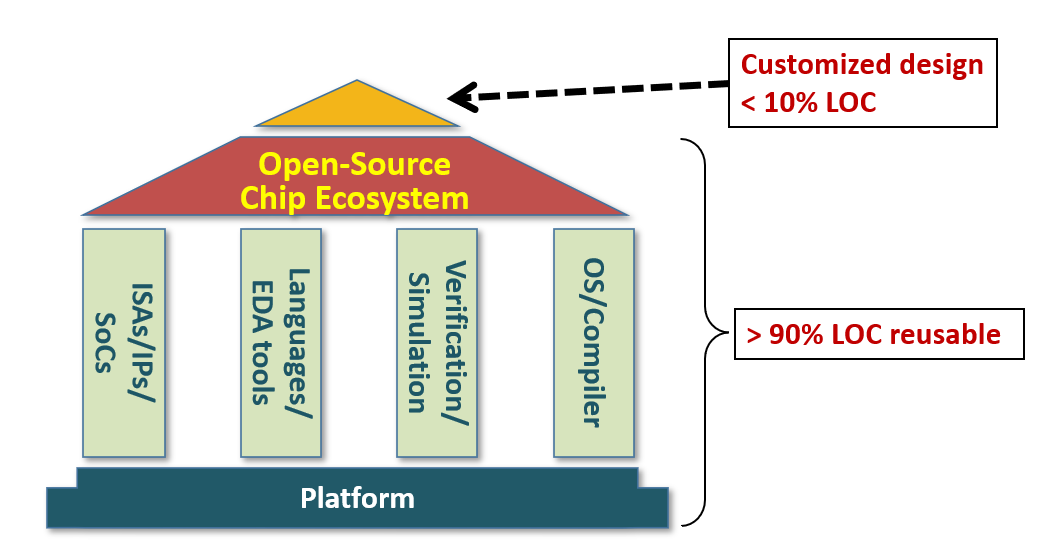

Seven years have passed since 2016, yet the vision of “making HW as easy to design/write as SW, open sourcing” remains vivid. What will the state of the open-source chip ecosystem be in another seven years? I firmly believe that this vision will eventually come to fruition, even if not by 2030. By that time, it is conceivable that up to 90% of the lines of code (LOC) in a chip design could be sourced from a self-contained open-source chip ecosystem, comprising plentiful open-source components for agilely constructing customized designs (see Figure 2).

Figure 2. Vision of Open-Source Chip Ecosystem

About the Author: Yungang Bao is a professor at the Department of Computer Science and Technology in University of Chinese Academy of Sciences (UCAS) and is the Chief Scientist of Beijing Institute of Open Source Chip (BOSC). His recent research focuses on open source and agile chip design.

Disclaimer: These posts are written by individual contributors to share their thoughts on the Computer Architecture Today blog for the benefit of the community. Any views or opinions represented in this blog are personal, belong solely to the blog author and do not represent those of ACM SIGARCH or its parent organization, ACM.