Hundreds of computer architects convened in the beautiful city of Columbus, Ohio to celebrate the 52nd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO). Led by general chairs Radu Teodorescu and DK Panda from The Ohio State University, Columbus welcomed visitors from all over the world with lovely weather, friendly volunteers, and two wonderful excursions to world-renowned Center of Science and Industry (COSI) and National Museum of the US Air Force. The technical program, put together by program chairs Tor Aamodt and Reetuparna Das, showcased key innovations across a wide range of computer architecture topics, from domain-specific accelerators to in/near-memory computing and from security to quantum computing.

Keynotes

This year’s MICRO had three inspiring keynote talks.

Krste Asanovic from UC Berkeley kicked off the main program sharing his experience on “Rejuvenating Computer Architecture Research with Open-Source Hardware”. With Moore’s Law becoming irrelevant, Asanovic made a strong case for the new vertical semiconductor business model where custom chip designs are needed for vertically integrated markets. He reflected on his early research of building custom architecture for neural algorithms in the early 90s, followed by the RISC-V revolution that has transformed the computing industry. He ended the keynote with a call to action for open hardware and tools to start the next wave of computing innovation.

Bill Dally from NVIDIA/Stanford emphasized the importance of “Domain-Specific Accelerators” for the future of computing. Dally pointed out that although mostly invisible, specialized hardware is already everywhere in today’s computing platforms. Using genomics and deep learning as two motivating examples, he highlighted the importance of algorithm-architecture co-design to improve end-to-end efficiency. Dally also motivated using GPUs as an accelerator platform together with customized compute blocks and hardware-aware programming models for future computing acceleration.

Lynn Conway from University of Michigan shared her sobering and powerful story of being “An Invisible Woman: The Inside Story Behind the VLSI Microelectronic Computing Revolution in Silicon Valley”. Reflecting on how women’s contributions in STEM are often erased from history, Conway shared her personal story of revolutionizing VLSI design that has led to a paradigm shift in the computing industry. In particular, she highlighted her transformative MIT’78 VLSI System Design Course she designed and taught as a Visiting Professor of EECS at MIT. Students, mostly seniors and graduate students, learned the basics of VLSI system design in the first half of the semester and then built and taped out real designs during the rest of the semester. Unfortunately, many of her contributions were not recognized until she came forward and “clawed her way to reappearance”. Her reflection on the disappearance of minorities’ contributions has led to Conway’s Conjecture: “Almost all people are blind to innovations, especially ones made by ‘others’ whom they do not expect to make innovations”, an important message that all of us should constantly remind ourselves.

Conference

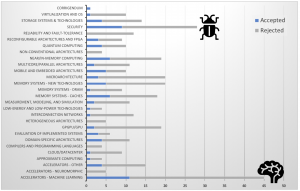

MICRO had an exceptionally strong program this year, thanks to the tremendous efforts put together by the program co-chairs Tor Aamodt and Reetuparna Das. 79 papers were accepted out of 344 submissions. In particular, the “Accelerators – Machine Learning” and “Security” topics, three sessions for each topic at MICRO this year, have the highest number of submissions: 45 and 28, respectively. The chairs also highlighted that 50% of papers with the primary topic in “Evaluation of Implemented Systems” were accepted, indicating an increasing focus on hardware prototyping and measured results in the computer architecture community. The “Mobile and Embedded Architectures” topic also has a 50% acceptance rate, followed by “Quantum Computing” with a 40% acceptance rate. You can see a detailed breakdown of the paper submissions below:

Six papers were nominated for the best paper award by the program committee, featuring a wide range of topics from multi-chip-module-based machine-learning hardware, multi-resolution storage for approximate computing, 3D data processing acceleration in mobile devices, protection of speculatively accessed data, FPGA-accelerated concurrency control for transactional memory, and statistical warming and sampling methodology. The best paper awards went to “Simba: Scaling Deep-Learning Inference with Multi-Chip-Module-Based Architecture” and “Speculative Taint Tracking (STT): A Comprehensive Protection for Speculatively Accessed Data”. The best paper runner-up was “Dynamic Multi-Resolution Data Storage”.

Two Test of Time awards went to: “Speculative Lock Elision: Enabling Highly Concurrent Multithreaded Execution” published at MICRO 2001 by Ravi Rajwar and James R. Goodman, and “Selective Cache Ways: On-Demand Cache Resource Allocation” published at MICRO 1999 by David H. Albonesi. Frederic Chong, Jangwoo Kim, David Wentzlaff, and Jishen Zhao were inducted into the MICRO Hall of Fame (https://www.sigmicro.org/micro-hall-of-fame/).

This year’s MICRO also featured three parallel sessions on Monday and Tuesday with 20 minutes per talk to make sure the authors have enough time to articulate their ideas and interact with the audience during Q&A. The lightning talk sessions on Monday and Tuesday helped the audience decide which talks to attend, and the poster sessions also provided more interactions between the authors and conference attendees.

The chairs also discussed the possibility of allowing authors to exchange comments with reviewers during the rebuttal period for future conferences at the business meeting. Recognizing a common pattern of the post-rebuttal discussion where the reviewers think “the authors’ response did not address my key concerns”, having a dialog between the authors and the reviewers could potentially help clarify misunderstandings. At the same time, there are concerns regarding fairness and the availability of authors/reviewers to allow a mechanism like this. Feedback is welcome from the communities on whether we could introduce such efforts in our future conferences.

Workshops and Tutorials

Workshop and Tutorial chair Samira Khan organized a wonderful program with nine workshops and tutorials, covering a wide range of topics in computer architecture research, from RISC-V research infrastructure, DNN compilation and modeling, OpenPiton+RISC-V, network-on-chip, agile chip design, high-performance deep-learning, machine learning + control theory. In particular, the 5th Career Workshop for Women and Minorities in Computer Architecture celebrated the achievements from women and underrepresented minorities in computer architecture, featuring a full-day program with inspiring keynotes, exciting research lightning talks and posters, and an engaging panel discussion on navigating graduate schools and career.

MICRO 2020 will be in Athens, Greece. See you next year!

About the Author: Sophia Shao is an Assistant Professor of the EECS department at University of California, Berkeley.

Editor’s note: Sophia was one of the recipients of the Best Paper Award at MICRO 2019.

Disclaimer: These posts are written by individual contributors to share their thoughts on the Computer Architecture Today blog for the benefit of the community. Any views or opinions represented in this blog are personal, belong solely to the blog author and do not represent those of ACM SIGARCH or its parent organization, ACM.