The memory wall has been a crucial power and performance bottleneck for computing systems. The growing gap between processor and memory speeds limits the energy-efficiency and performance of almost all forms of computing systems. As technology scales down, the speed gap widens and the number of interconnect transistors packed per unit of area increases; therefore, the parasitic capacitance of wires further increases the delay of data movement. Such intrinsic limitations of electronic devices make it challenging for conventional electronic memories to conquer the memory wall. For example, DRAMs and SRAMs relying on depleted Silicon On Insulator (SOI) or shrunk 14nm Tri-Gates hardly achieve up to 2GHz and 5GHz. To address this problem, numerous researchers have considered alternative technologies for memory systems. One such technology is the recently introduced optical random access memory (Optical RAM) that employs light instead of electric charge for storing information.

Optical Flip-Flop

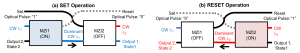

A general view of an optical flip flop is shown in Figure 1. The key operation of the optical flip-flop is based on the reconfigurability of an optical device called Mach–Zehnder interferometer (MZI). A typical MZI device can be set to steer light signals from one source to one or multiple destinations. As shown in Figure 1, two coupled MZIs form an optical flip-flop (MZI1 and MZI2). Each MZI is connected to an external source of continuous wave (CW) bias light with a specific wavelength (λ1 for MZI1 and λ2 for MZI2). Light pulses may be sent through the “Set” and “Reset” ports to change the flip-flop’s state. By sending a light pulse via the “Set” port, MZI1 is set to ON, thereby allowing its input CW signal (λ1) to travel from MZI1 to MZI2. This signal forces MZI2 to operate in its OFF state. In this state, MZI2 doesn’t allow its input CW signal (λ2) to travel between the two MZIs. In contrast, sending light pulses through the “Reset” port sets MZI2 to ON. As a result, MZI2 allows its input CW signal (λ2) to travel from MZI2 to MZI1. For each of these flip-flop states, the signal traveling between the two MZIs is called the dominant signal. By definition, the flip-flop represents a logical “1” if the dominant signal is λ1 and a logical “0” if the dominant signal is λ2. In other words, the two MZIs are used to send both CWs (λ1 and λ2) to either output 1 (logical “1”) or output 2 (logical “0”). As long as the continuous signals are fed to the flip-flop, the cell can retain the state of MZIs.

Figure 1. Overview of two states of an optical flip-flop

Basic Structure of an Optical Static RAM

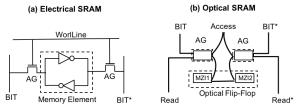

Inspired by the structure of a conventional SRAM cell (Figure 2a), the first optical static RAM cell was invented by Pleros et al. in 2008 (Figure 2b). The electrical SRAM cell includes two access transistors (a.k.a. access gates AG) controlled by a wordline to enable reading/writing the contents of a charge-based memory element. Prior to every access, the wordline is activated to establish two electrical paths between the memory element and bitlines (denoted by BIT and BIT* in the figure). The bitlines carry charge from/to the cell and if necessary change the contents. The SRAM element is able to retain its contents even after disconnecting the access paths. In contrast, the optical static RAM includes an optical flip-flop and two access gates. The optical access gates are used to access the optical flip-flop.

Figure 2. Conventional SRAM (a) vs. optical RAM (b) cells

The optical RAM cell is designed to operate in three states: hold, read, and write. The memory cell transitions to the hold state by setting Access to 0 (i.e., no light signal). In the hold state, the optical flip-flip remains unchanged. During a write operation, Access is set to 1. Therefore, the Bit and Bit* will be connected to the Set and Reset ports of the flip-flip, respectively. Setting BIT to 0 and BIT* to 1 results in resetting the flip-flop, thereby writing a logical “0”. In contrast, a logical “1” is written to the optical flip-flop by setting BIT and BIT* to 1 and 0. For an optical read, the access port is set to 1. The logical value stored in the memory cell is determined by detecting the dominant signal of the flip-flop through output ports Read and Read*. A light signal at the Read port indicates a 1; whereas, a light signal at the Read* port indicates a 0. This optical RAM cell operates at 5Gb/s.

New Generation of Optical RAMs

Recently, researchers from Greece have examined an all-optical RAM cell that performs both read and write operations at 10Gb/s. This is a 2X improvement compared with its prior technology. The new RAM cell is made of a flip-flop that is composed of a new photonic crystal (Indium phosphide) and an optical access gate. Indium phosphide has a high electron velocity property and hence it is a good fit for optical high-speed memories. In the proposed design, the switching time at the access gate output becomes 20ps that adds only a small jitter penalty to the integrated Indium Phosphide optical flip-flop latching of 70ps. Hence, the access latency is less than 100ps, enabling a 10Gb/s optical RAM cell.

Architectural Implications

Table 1. Comparison of state-of-the-art RAM cells using different technologies.

| Work | IBM-65nm | MIT-28nm | Intel-22nm | Intel-14nm(1) | Intel-14nm(2) | ASU-7nm | OpticalRAM-2019 | OpticalRAM-Future |

| Area(um2) | 0.9 | 0.23 | 0.108 | 0.049 | 1.84 | 0.035 | 1.2e+7 | ~um2 |

| Frequency(GHz) | 5.3 | 0.090 | 4.6 | 4.0 | 1.0 | 2.0 | 10.0 | 10.0 |

Table 1 compares state-of-the-art RAM cells in different technologies. The last two columns are optical RAM while others are electrical RAMS. A 65nm CMOS electronic RAM can operate at a 5.3GHz frequency. By shrinking the transistor sizes, the power consumption of conventional electronic RAMs becomes more significant. An optical RAM cell consumes 200pJ/bit while it consumes about 12mm2 of die area. The size and energy of current optical RAM prototypes are larger than electronic RAMs (e.g., MIT-18nm is about 52 fj). However, their higher speed compared to electronic RAMs may be appealing to high-performance supercomputers. Furthermore, the latency of electronic memory cells has been improved by about 30% during the last two decades. Currently, the latency of state-of-the-art DDR4 is about 10 ns. However, the latency of the optical memory cell is about 100 ps, which is a 100X improvement compared with the electronic memories. In addition, more complex optical technologies like III-V-onSOI PhC that are evaluated just for single FF or AG, encourage us to look forward to the future generations of optical RAMs with a few fJ/bit energy and a few μm2 area requirements. Therefore, optical RAM may be considered as a promising alternative to electric RAMs where fast access times are necessary. It is worth mentioning that optical RAM is expected to be a more viable solution for optical processors; otherwise, converting information between the optic and electronic domains would be a significant challenge as it impacts the access latency considerably. Although some efforts have been made to build special-purpose optical processors, such as Fathom Computing for neural networks, there is still a long way to build a general-purpose optical processor.

About the authors: Payman Behnam is a graduate researcher at the Energy-Efficient Computer Architecture Laboratory, University of Utah, where he is involved in designing novel memory systems and energy-efficient accelerators for computer vision and machine learning applications. Mahdi Nazm Bojnordi is an assistant professor of the School of Computing at the University of Utah, Salt Lake City, UT.

Disclaimer: These posts are written by individual contributors to share their thoughts on the Computer Architecture Today blog for the benefit of the community. Any views or opinions represented in this blog are personal, belong solely to the blog author and do not represent those of ACM SIGARCH or its parent organization, ACM.